0769-28639799

0769-23380137

江晟電機(jī)產(chǎn)品

聯(lián)系我們

江門市江晟電機(jī)廠有限公司

熱線電話:0769-28639799

熱線電話:0769-23380137

傳真電話:0769-81380536

網(wǎng)? ? ? ? 址:www.khvost.com

郵? ? ? ? 箱:583653599@qq.com

地? ? ? ? 址:東莞市萬江區(qū)莞穗大道166號(hào)

熱線電話:0769-28639799

熱線電話:0769-23380137

傳真電話:0769-81380536

網(wǎng)? ? ? ? 址:www.khvost.com

郵? ? ? ? 箱:583653599@qq.com

地? ? ? ? 址:東莞市萬江區(qū)莞穗大道166號(hào)

公司新聞

江門市江晟電機(jī)廠有限公司 > 公司新聞 >

分析江晟電機(jī)驅(qū)動(dòng)電路原理

發(fā)布時(shí)間: 2016-09-12 ? ? 文章來源:www.khvost.com ? ? 作者江晟電機(jī)

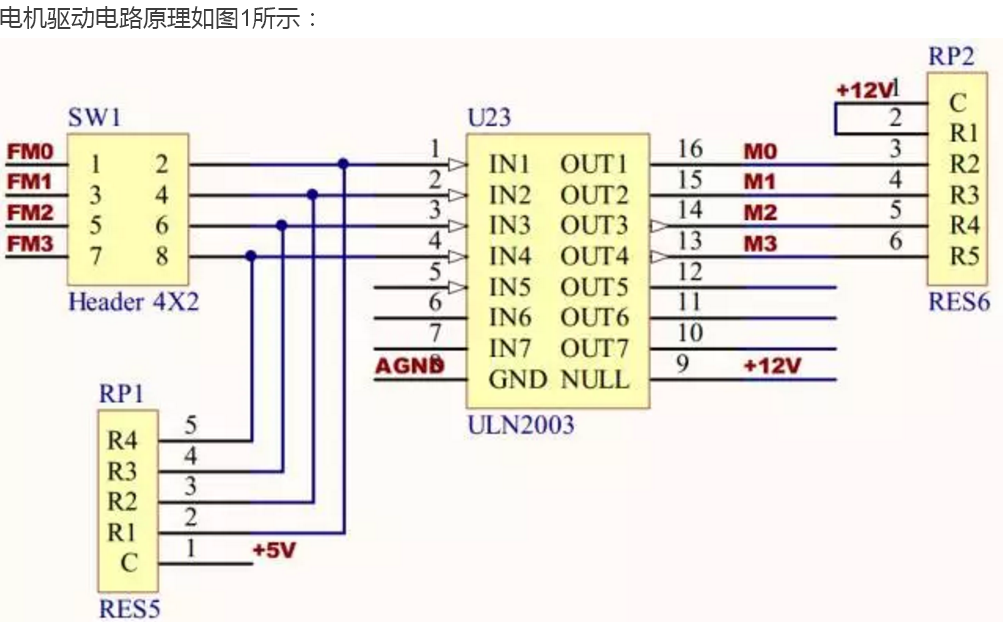

江晟電機(jī)驅(qū)動(dòng)電路原理如圖1所示:

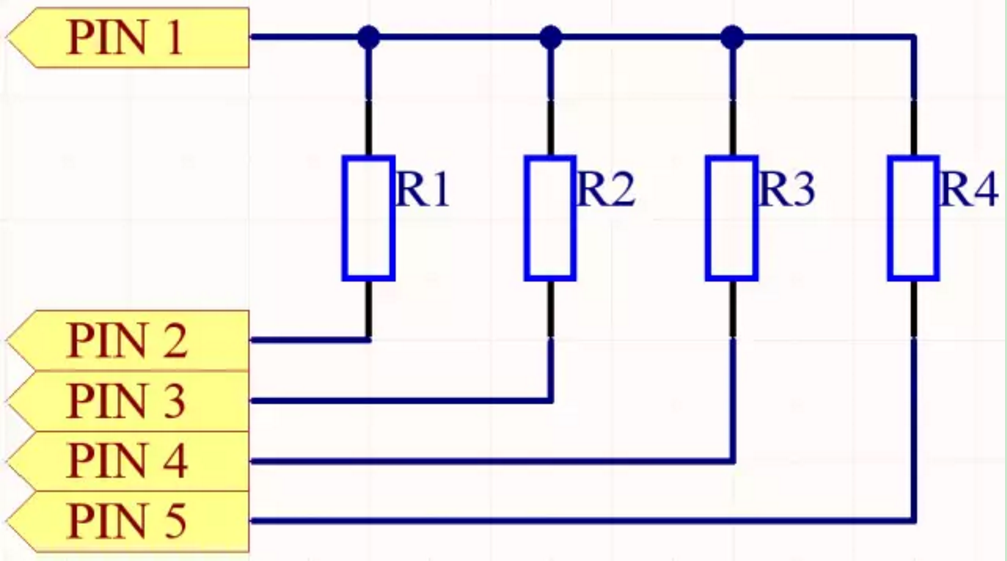

圖1中Header4X2為4排2列插針,F(xiàn)M0~3為FPGA芯片I/O輸出口,加入的插針給予一個(gè)可動(dòng)的機(jī)制,在需要使用時(shí)才用跳線帽進(jìn)行相連,提高I/O口的使用效率。RES5是五端口排阻,內(nèi)部集成了4個(gè)等阻值且一端公共連接的電阻,PIN1是公共端,PIN2~5為排阻的輸出端,排阻原理圖如圖2所示:

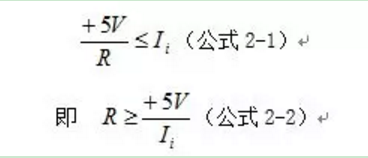

該排阻公共端接電源,即上拉電阻形式,作用是增強(qiáng)FPGA芯片I/O口(以下簡稱I/O口)的驅(qū)動(dòng)能力,實(shí)際上就是增加I/O輸出高電平時(shí)輸出電流的大小。當(dāng)I/O輸出高電平時(shí),+5V電源經(jīng)排阻與IN1~4相連,相當(dāng)于為I/O提供一個(gè)額外的電流輸出源,從而提高驅(qū)動(dòng)能力。當(dāng)I/O輸出低電平時(shí),可將I/O近似看做接地,而IN1~4因與I/O由導(dǎo)線直接相連,因此直接接受了I/O的低電平輸出信號(hào)。此時(shí),+5V電源經(jīng)排阻R、I/O內(nèi)部電路(電阻近似為零)后接地,因此該路的電流不能大于I/O的拉電流(Ii)最大值,有公式2-1:

由公式2-2可以得出排阻的取值范圍。

該上拉電阻除了提高驅(qū)動(dòng)能力外,還有一個(gè)作用,就是進(jìn)行電平轉(zhuǎn)換。經(jīng)查,ULN2003的接口邏輯為:5V-TTL,5V-CMOS邏輯。而在3.3V供電的情況下,I/O口可以提供3.3V-LVTTL,3.3V-LVCMOS,3.3V-PCI和SSTL-3接口邏輯電平。因此,需要外接5V的上拉電阻將I/O電平規(guī)格變成5V電平邏輯。

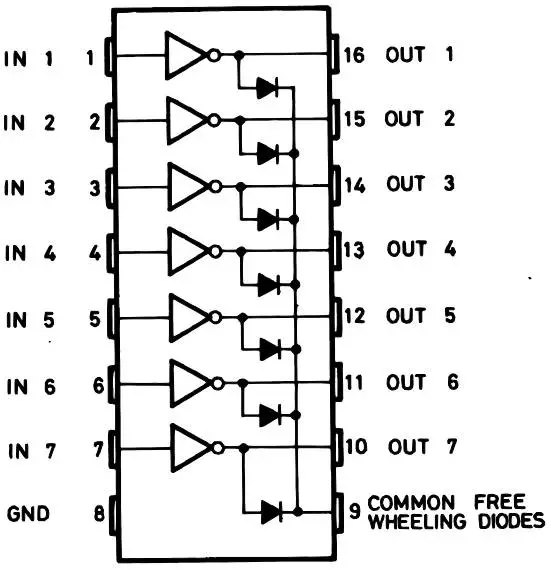

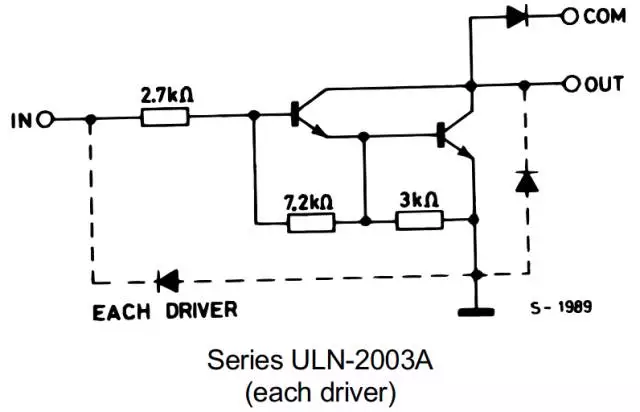

芯片ULN2003內(nèi)部集成7組達(dá)林頓管,專門用于提高驅(qū)動(dòng)電流,芯片引腳間邏輯如圖3所示:

由于I/O電流遠(yuǎn)遠(yuǎn)不足以驅(qū)動(dòng)江晟電機(jī),因此需要外接該芯片驅(qū)動(dòng)江晟電機(jī),ULN2003內(nèi)部集成的達(dá)林頓管電路如圖4所示。達(dá)林頓管的形式具有將弱點(diǎn)信號(hào)轉(zhuǎn)化成強(qiáng)電信號(hào)的特點(diǎn),I/O電平邏輯從PININ輸入,通過達(dá)林頓管控制PIN9(COMMON)端輸入的強(qiáng)電信號(hào)按照I/O信號(hào)規(guī)律變化。值得注意的是:ULN2003輸出邏輯將與輸入邏輯相反,編程時(shí)應(yīng)該注意該特點(diǎn)。

RES6是六端口排阻,內(nèi)部集成了5個(gè)等阻值且一端公共連接的電阻,PIN1是公共端,PIN2~6為排阻的輸出端,原理圖與接法說明可參考上述圖2-2,排阻取值范圍計(jì)算參見公式2-2,此處不再贅述。值得注意的是:RES6的PIN1與PIN2相連,是因?yàn)槎喑隽艘粋€(gè)不使用的電阻,為了避免PIN2懸空,因此將PIN2與PIN1(公共端)相連,即PIN2對(duì)應(yīng)的電阻被短路,從而既避免的懸空的引腳,又能使該電阻失效。

標(biāo)簽:江晟電機(jī)

標(biāo)簽:江晟電機(jī)